Sigetest – fault simulation system for digital devices

The Sigetest fault simulation system allows designers to simulate test sequences and analyze fault coverage and test quality for complex digital devices. Sigetest supports output of modern synthesis tools (Synplicity® Synplify, Synopsys® Design Compiler) in form of VHDL gate-level net lists. Verilog design entry for Sigetest is in development.

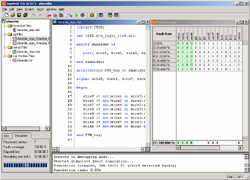

Sigetest contains event-based fault-free simulation algorithm, two fault simulation algorithms: serial and deductive. Simulation kernel handles RAM models, black boxes (basic triggers, three-state buffers, multi-driver connections). Simulation alphabet is X01Z. Sigetest has friendly MDI GUI. The output is the fault coverage in form of log file and multi-sign fault table, test quality, simulation statistics.

Sigetest has beta version status.

Inculcation: system is integrated with educational process of Kharkiv National University of Radio Electronics for specialties “System Programming”, “Computer Systems and Networks”, “Specialized Computer Systems” in courses “Design for testability”, “CAD”, “Diagnosis of digital devices”.

Sigetest system has been rewarded with diploma in Intel® CAD competition in 2003(http://www.intel.com/ru/pressroom/2003/061001.htm).

Technologies: C++ (STD, STL, QT Library), VHDL (IEEE.STD), Verilog.

Man-days: 400

|