IP-Core for analysis of Russian adjectives

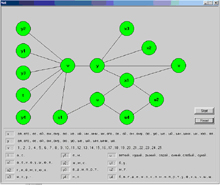

For implementation proposed net model which executes Russian language adjective analysis. Net allows defining other properties of word based on defined properties. VHDL language is used for formal description of specification and design development. Model represented as net: nodes are sets of word attribute values, arcs are relations between them. Initially each node contains complete set of attributes, typical for it. Iterative process of parallel data transfer to adjacent nodes is executing when activates one or more node by data changing or putting in initial values. The process stops when a stability criterion is reached. Stability criterion is reaching identical state for all nodes in two adjacent steps (differences are absent in two adjacent steps).

Tools: Synplicity Synplify Pro is used for synthesis. Xilinx ISE WebPack is used for implementation. Target device is Xilinx FPGA XCV300E.

For suitable analysis of device algorithm process, interface C++ program was developed. Due to the PLI (Programming Language Interface) library data can be transferred to and from the model in simulation process.

Technologies: VHDL (IEEE.STD, VHPI), Verilog (PLI), C++ (STD, WinAPI)

Man-days: 60

|